LimeSDR X3

LimeSDR X3

LimeSDR X3 is a full size PCIe Gen 2 x4 card that integrates three Lime Microsystems LMS7002M transceivers, which may be used to simultaneously support 4G, 5G and adaptive digital pre-distortion (ADPD) for power amplifier (PA) linearisation. LimeSDR X3 is the radio transceiver platform used in turnkey systems such as LimeNET 2.0 and LimeNET Mini 2.0.

While designed with cellular networks in mind, LimeSDR X3 may be used to support any air interface and in applications such as Digital Video Broadcasting (DVB), for example.

As standard LimeSDR X3 is supplied with RF matching networks optimised for popular 4G and 5G bands, but the matching networks may be optimised for other frequency bands upon request.

An advanced radio platform for high performance applications

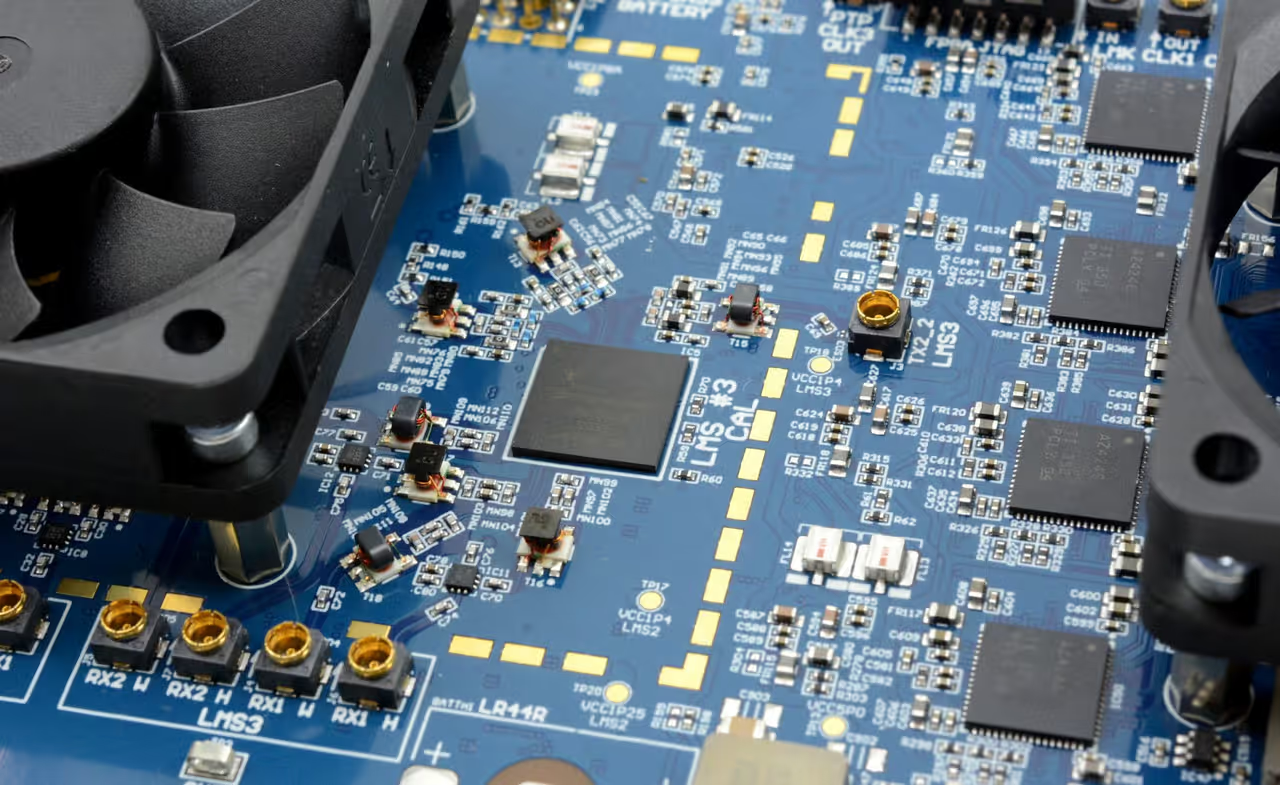

LimeSDR X3 employs an AMD Artix-7 FPGA with 215K logic elements and 740 DSP slices, plus three LMS7002M transceivers, which are typically designated for 4G, 5G and ADPD use.

The 5G designated transceiver utilises high speed ADCs and DACs and is able to support up to 100MHz RF bandwidth 2x2 MIMO. RF switches on the board also enable this to be connected to the third transceiver, which is intended for use with ADPD and for calibration purposes.

The 4G and 5G designated transceivers both feature PA drivers in their transmit paths.

LimeSDR X3 is the target platform for Lime Adaptive Digital Pre-Distortion (LimeADPD), a fully open source software and FPGA gateware implementation which provides not only ADPD, but also crest factor reduction (CFR) and an equaliser for I/Q imbalance correction and gain flattening.

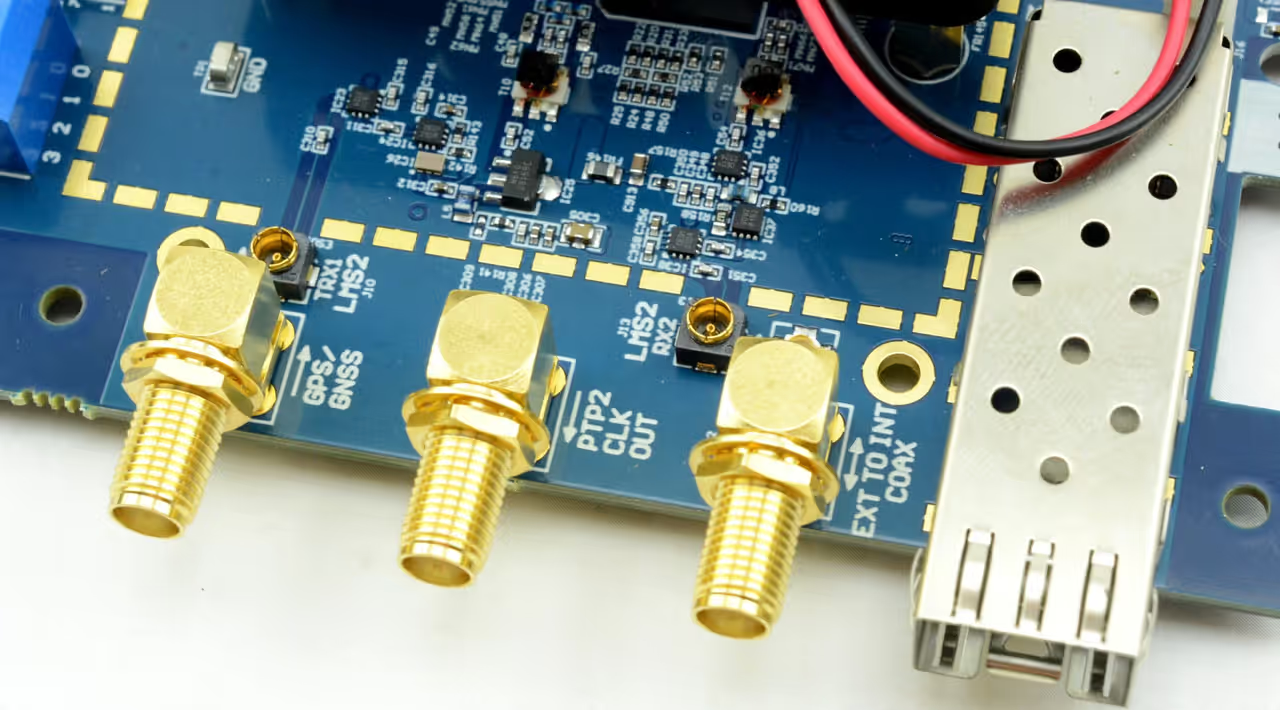

White Rabbit support for high precision time and frequency transfer

LimeSDR X3 can be configured to support White Rabbit Precision Time Protocol (WR PTP) in order to provide high accuracy time and frequency transfer, enabling applications to scale up to thousands of nodes and with up to 10km between network elements.

White Rabbit timing networks employ fibre optic media and are able to achieve high precision synchronisation, thanks to using IEEE 1588 PTP together with Synchronous Ethernet (SyncE) for L1 syntonisation, plus phase measurement for link delay calculation. This results in a sub-nanosecond synchronisation accuracy, compared with sub-microsecond for IEEE 1588-2008.

LimeSDR X3 features an SFP cage for use with White Rabbit (a 1000BASE-BX10 standard bi-directional transceiver with a single LC connector is recommended). For evaluation purposes and where only two nodes are required, two LimeSDR X3 boards may be directly connected, with one configured as PTP grandmaster. A White Rabbit switch is required with three or more nodes.

Specifications

#1 (4G): Lime Microsystems LMS7002M:

- Configuration: MIMO (2xTX, 2xRX)

- Frequency range: 30 MHz – 3.8 GHz

- Bandwidth: 120 MHz

- Sample depth: 12 bit

- Sample rate: 120 MSPS SISO / 90 MSPS MIMO

- Transmit power: max 10 dBm (depending on frequency)

#2 (5G): Lime Microsystems LMS7002M with external ADCs + DACs:

- Configuration: MIMO (2xTX, 2xRX)

- Frequency range: 300 MHz – 3.8 GHz

- Bandwidth: 100 MHz (flat response)

- Sample depth: 14 bit ADC and 16 bit DAC

- Sample rate: Up to 160 Msps ADCs / 250 Msps DACs

- Transmit power: max 10 dBm (depending on frequency)

#3 (calibration/ADPD): Lime Microsystems LMS7002M with external ADCs:

- Configuration: MIMO (2xTX, 2xRX)

- Frequency range: 30 MHz – 3.8 GHz

- Bandwidth: 120 MHz

- Sample depth: 14 bit ADC / 12 bit DAC

- Sample rate: Up to 160 Msps ADCs

- Transmit power: max 10 dBm (depending on frequency)

Artix-7 XC7A200T:

- 676-FCBGA (27x27) package

- 215,360 logic elements

- 740 DSP slices

- 13 Mb block RAM

- x4 Gen 2 PCIe interface

- 10 clock management tile (CMT), each containing one MMCM and one PLL

- 256 Mbit FPGA configuration flash

- 4x 128Kbit (16K x 8) EEPROM (for each RF transceiver and FPGA data)

- Temperature sensor

- Crypto Authentication Device

- GNSS receiver

- 30.72MHz (default) VCOCXO and 38.4MHz (optional) VCTCXO

- VCOCXO disciplined (synchronisation) options:

- GNSS PPS signal

- Reference clock input or onboard DAC

- White Rabbit PTP (slave or grandmaster)

- Clock generator/PLL for baseband DACs, ADCs

- 2x PMOD headers (0.1” pitch) connected to FPGA

- 4x dual color (RG) LEDs connected to FPGA

- 4x Switches connected to FPGA

- Coaxial RF (SMA and uFL/MMCX) connectors

- uFL/MMCX connectors and headers for reference clock IN/OUT, GNSS antenna

- 12V header for powering external devices

- Fan headers

- FPGA JTAG connector (2mm pitch)

- Dimensions: 232.5mm x 106.7mm (9.15” x 4.2”) excluding connectors

- 12V 6-pin PCIe power connector